Why High-Frequency PCBs Fail Even When RF Simulations Look Perfect

High-frequency PCB design is one of the most failure-prone disciplines in electronics engineering.

Many RF designs perform exactly as expected in simulation, only to show unexpected loss, phase drift, instability, or coupling issues once fabricated and assembled. These failures often appear:

· At higher temperatures

· At the band edges

· After scaling from prototype to volume production

· When switching PCB suppliers or laminate batches

The root cause is rarely a single mistake.

Instead, failures emerge from a gap between RF theory and manufacturing reality.

At high frequencies, every physical detail matters—not only trace geometry, but also copper roughness, resin distribution, lamination accuracy, and assembly-induced variation.

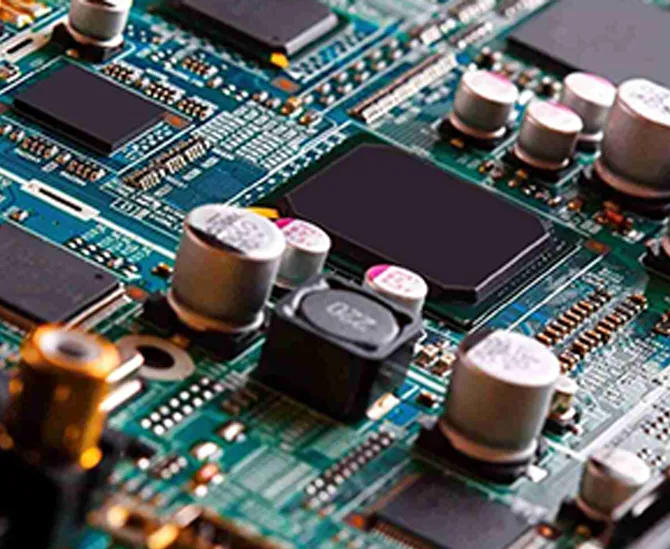

Understanding RF Loss Mechanisms in Real PCBs

High-frequency signal degradation is dominated by loss, not logic timing.

2.1 Dielectric Loss (Df)

Dielectric loss increases exponentially with frequency.

Even small differences in dissipation factor (Df) lead to measurable insertion loss and phase error at GHz frequencies.

Common misconceptions:

· “Low Dk is enough”

· “FR-4 works up to X GHz”

In reality, Df stability across frequency and temperature is far more important than nominal values.

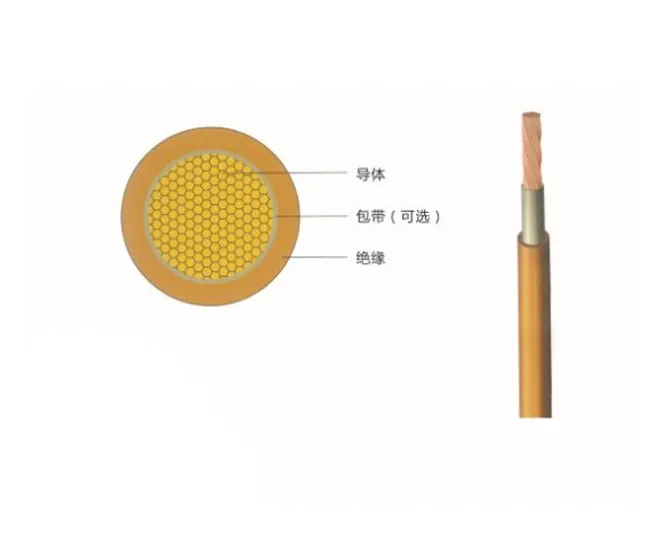

2.2 Conductor Loss and Copper Roughness

At high frequencies, current flows primarily on the conductor surface due to the skin effect.

Copper roughness significantly increases effective path length, resulting in:

· Higher insertion loss

· Increased phase distortion

· Reduced Q factor

Standard copper foils optimized for mechanical adhesion often perform poorly in RF applications.

2.3 Radiation and Leakage Loss

Discontinuous return paths, poor grounding, and open structures cause RF energy to radiate instead of propagating.

This loss is rarely predicted accurately in circuit-level simulation but becomes dominant in physical layouts.

Material Selection Failures: Where Most RF Designs Go Wrong

Material choice is the single most critical decision in high-frequency PCB design—and also the most misunderstood.

3.1 Over-Reliance on FR-4

FR-4 is attractive due to cost and availability, but it suffers from:

· High and inconsistent Df

· Wide Dk variation

· Strong temperature dependence

Using FR-4 beyond its practical frequency limit introduces unpredictable behavior that no amount of tuning can fully correct.

3.2 Misinterpreting Laminate Datasheets

Datasheet values are often:

· Measured at specific frequencies

· Averaged across batches

· Taken under ideal test conditions

Designers who assume datasheet values represent production reality often face lot-to-lot variation issues.

3.3 Ignoring Resin System Stability

Different resin systems within the same laminate family can behave very differently under:

· Thermal cycling

· Humidity exposure

· Long-term aging

These effects accumulate over product lifetime, not just initial testing.

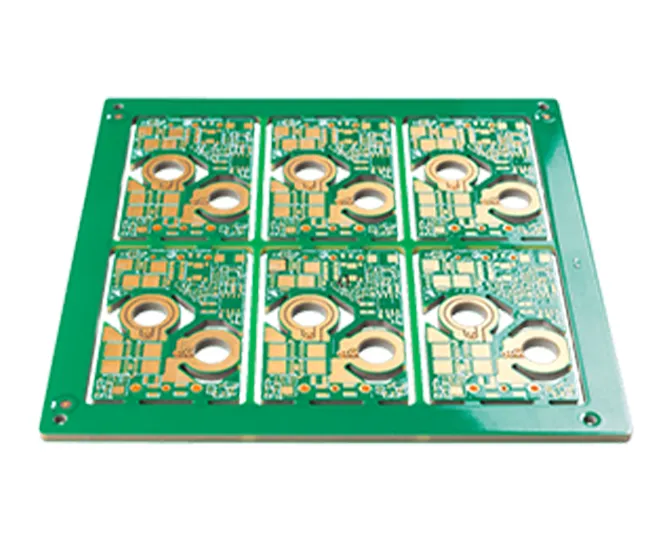

Hybrid Stackup Design: Performance Gains and Yield Risks

Hybrid stackups—combining RF laminates with FR-4—are common in cost-sensitive designs.

While effective in theory, they introduce significant manufacturing complexity.

4.1 Lamination Mismatch Risks

Different materials expand, flow, and cure differently during lamination.

This can cause:

· Layer misregistration

· Resin starvation

· Impedance drift

· Internal stress accumulation

These issues often do not appear in small prototype runs.

4.2 Yield Collapse in Volume Production

Hybrid stackups frequently show acceptable yields at low volume, then experience:

· Increased scrap rates

· Inconsistent impedance

· Delamination risks

Designs that lack margin are especially vulnerable.

4.3 DFM Considerations for Hybrid Stackups

Effective hybrid designs require:

· Early fab involvement

· Validated lamination cycles

· Conservative design margins

· Material availability planning

Ignoring these factors shifts risk from engineering to production.

RF + Digital Coupling: The Silent Performance Killer

Modern RF boards rarely contain RF alone.

High-speed digital interfaces, power management, and control logic coexist with sensitive RF structures.

5.1 Ground and Return Path Conflicts

Digital return currents often share reference planes with RF signals, introducing:

· Noise modulation

· Phase jitter

· Spurious emissions

Poor plane partitioning is a common root cause of degraded RF performance.

5.2 Harmonic Coupling and Spur Generation

High-speed clocks generate harmonics that can fall directly into RF bands.

Without proper isolation, these harmonics:

· Appear as spurs

· Reduce signal-to-noise ratio

· Complicate compliance testing

5.3 Layout-Level Mitigation Strategies

Successful RF + digital coexistence requires:

· Controlled plane segmentation

· Strategic via placement

· Physical separation aligned with frequency sensitivity

These decisions must be made early—after routing, it is usually too late.

Manufacturing Constraints Unique to High-Frequency PCBs

High-frequency performance is extremely sensitive to manufacturing variation.

6.1 Etching Tolerance and Line Geometry

Small changes in trace width or edge profile cause:

· Impedance deviation

· Phase mismatch

· Increased loss

Fine-line RF designs push etching capability limits.

6.2 Dielectric Thickness Variation

Prepreg flow variation affects dielectric height, which directly impacts impedance and phase delay.

Designs without margin experience unpredictable performance shifts.

6.3 Surface Finish Impact

Surface finishes influence conductor loss:

· ENIG introduces additional loss

· Immersion silver performs better but has handling risks

· Bare copper is rarely practical

Finish choice is a performance decision, not just a cost decision.

Get to know more about PCB Fabrication Process: PCB Fabrication Process: From Design Data to Finished Circuit Boards

DFA: Assembly Effects on RF Performance

Assembly-related issues often escape RF design reviews.

7.1 Solder Mask and Component Interaction

Solder mask thickness and dielectric properties alter effective impedance at RF frequencies.

Component placement accuracy affects:

· Matching networks

· Differential symmetry

· Phase balance

7.2 Reflow-Induced Material Stress

Thermal cycles during reflow can:

· Change laminate properties

· Induce micro-cracking

· Alter long-term RF stability

Ignoring assembly effects leads to performance drift after production.

Failure Case Study: RF Board That Passed Lab Tests but Failed in the Field

A typical real-world example:

· Prototype: 20 units, hand-assembled

· Performance: within spec

· Production: 3,000 units, automated assembly

Field failures show:

· Increased insertion loss at high temperature

· Phase instability over time

Root cause analysis identifies:

· Hybrid stackup sensitivity

· Copper roughness variation

· Assembly-induced stress

The design had no margin for manufacturing reality.

Cost vs Performance Trade-Offs in High-Frequency Design

High-frequency PCBs circuit boards are expensive—but poorly planned RF designs are far more expensive.

Cost drivers include:

· Specialty laminates

· Tight fabrication tolerances

· Increased scrap risk

· Extended validation cycles

However, over-designing also drives unnecessary cost.

The goal is controlled performance, not theoretical maximums.

Smart trade-offs:

· Use RF materials only where needed

· Limit hybrid complexity

· Design for yield, not perfection

Procurement and Supply Chain Impact

Material availability affects long-term product stability.

Single-source laminates increase risk of:

· Lead-time delays

· Forced redesigns

· Performance variation

Early supply chain alignment reduces re-spin probability.

Engineering Checklist for Reliable High-Frequency PCBs

· Identify dominant loss mechanisms

· Select materials based on stability, not marketing

· Validate hybrid stackup manufacturability

· Isolate RF and digital return paths

· Design with fabrication tolerance margin

· Align RF performance targets with volume production capability

How China 365PCB Supports High-Frequency PCB Projects

As a leading OEM PCB manufacturer, 365PCB supports RF projects through:

· Material selection consultation

· Hybrid stackup DFM review

· Process-aware impedance control

· Volume-production-aligned validation

The focus is repeatable RF performance, not lab-only success.

Final Thoughts: RF Success Is Built on Manufacturing Reality

High-frequency PCB design is not defined by simulation results alone.

It is defined by how well theory survives fabrication, assembly, and time.

Designs that succeed do so because they respect loss mechanisms, material behavior, and production constraints from the beginning.

Engineering CTA (Low-Key, Professional)

If your RF design must remain stable from prototype through volume production, early coordination between design and manufacturing is essential.

Our engineering team is available to review materials, stackups, and DFM risks before fabrication begins.

David Li

David Li is the Technical Communications Director at China 365PCB, with over 15 years of hands-on experience in the PCB and electronics manufacturing industry. Holding a Master’s degree in Electrical Engineering, he has worked extensively in both R&D and manufacturing roles at leading multinational electronics firms in Shenzhen before joining our team.

His expertise spans high-speed digital design, advanced packaging (HDI, Flex), and automotive-grade reliability standards. David is passionate about bridging the gap between design intent and production reality—a philosophy that aligns perfectly with 365PCB’s mission to deliver seamless, rapid, and fully-integrated manufacturing solutions.

Follow David’s insights on PCB technology trends and best practices here on the 365PCB Knowledge Hub.

English

English