Why EMI / EMC Problems Appear When It Is Already Too Late

EMI and EMC failures are among the most expensive surprises in electronics development.

Unlike functional bugs, EMI issues usually appear:

· After the PCB is fabricated

· After the enclosure is finalized

· During certification testing

· When schedules and budgets are already committed

At this stage, fixes are limited to:

· Shielding cans

· Ferrite beads

· Ground stitching “band-aids”

· Costly PCB re-spins

The harsh reality is:

Most EMI problems are designed in long before the first prototype is built.

Successful EMI design is not about suppression—it is about preventing noise generation in the first place.

What EMI and EMC Really Mean at the PCB Level

EMI (Electromagnetic Interference) describes unwanted emissions generated by a system.

EMC (Electromagnetic Compatibility) describes a system’s ability to:

· Limit its own emissions

· Remain immune to external interference

At the PCB level, EMI and EMC are determined by:

· How currents flow

· How return paths are managed

· How energy couples between structures

Compliance is therefore a current-control problem, not a filtering problem.

Fundamental EMI Generation Mechanisms

3.1 Differential-Mode Radiation

High-speed signals with large current loops radiate energy.

Common causes:

· Long signal-return loops

· Discontinuous reference planes

· Poor stackup design

Differential-mode radiation dominates at lower frequencies.

3.2 Common-Mode Radiation

Common-mode noise is the primary cause of EMI failures.

It is generated when:

· Differential signals become unbalanced

· Return paths are interrupted

· Signals reference multiple grounds

Common-mode currents easily excite cables, connectors, and enclosures.

Why EMI Problems Are Often Misdiagnosed

EMI failures rarely point clearly to their root cause.

Typical misdiagnoses include:

· “The cable is bad”

· “The enclosure is not shielded enough”

· “The power supply is noisy”

In reality, cables and enclosures usually amplify noise that already exists on the PCB board.

Fixing EMI at the enclosure level is expensive and often incomplete.

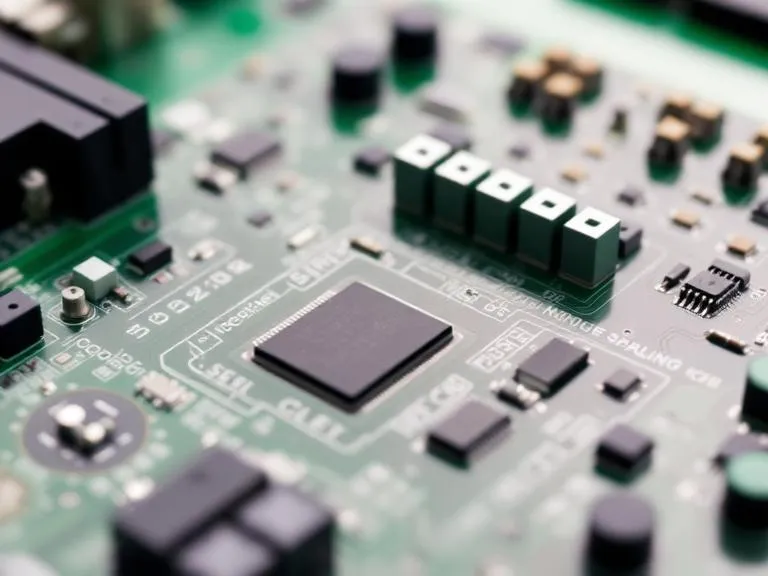

Stackup Design: The Foundation of EMI Control

EMI success starts with stackup design.

A good stackup:

· Minimizes loop area

· Provides continuous reference planes

· Controls impedance

· Reduces mode conversion

5.1 Common Stackup Mistakes

· Too few ground planes

· Signal layers not adjacent to reference planes

· Power planes separated without stitching

· Asymmetric stackups causing warpage and imbalance

No amount of routing optimization can fully compensate for a poor stackup.

Get to know more about PCB stackup design: PCB Stackup Design The Structural Foundation of Signal Integrity, EMI Control, and Manufacturing Reliability

Routing Practices That Directly Affect EMI

6.1 Return Path Continuity

Every signal must have a clear, uninterrupted return path.

Plane splits under high-speed signals force return currents to detour, increasing loop area and radiation.

6.2 Layer Transitions and Via Stitching

When signals change layers:

· Return paths must follow

· Stitching vias must be placed close to signal vias

Missing stitching vias are a common source of EMI spikes.

Power Distribution Network (PDN) and EMI Interaction

Power integrity and EMI are inseparable.

A noisy PDN causes:

· Jitter

· Ground bounce

· Common-mode conversion

7.1 Decoupling Strategy Failures

Common mistakes include:

· Too few capacitors

· Incorrect capacitor values

· Poor placement relative to IC pins

Decoupling is about loop inductance, not capacitance value alone.

Manufacturing Variations That Affect EMI Performance

EMI simulations assume ideal geometry.

Manufacturing delivers statistical variation.

8.1 Copper Thickness and Roughness

Copper variation affects:

· Impedance

· Return current distribution

· Radiation characteristics

8.2 Dielectric Thickness Variation

Dielectric variation alters:

· Signal velocity

· Mode conversion behavior

· Resonant frequencies

Designs without margin fail unpredictably across lots.

DFM: Designing for EMI-Stable Manufacturing

EMI-robust designs must tolerate fabrication variation.

9.1 Practical DFM Guidelines for EMI

· Conservative trace spacing

· Controlled impedance with margin

· Avoid unnecessary plane splits

· Maintain symmetry across layers

Designs that push fab limits increase EMI risk.

DFA: Assembly Effects on EMI Behavior

Assembly can significantly affect EMI.

10.1 BGA Voids and Ground Integrity

Solder voids under BGAs disrupt ground continuity, increasing common-mode noise.

10.2 Connector and Shield Placement

Misaligned connectors or poorly grounded shields become efficient antennas.

Assembly quality directly affects EMC margin.

Failure Case Study: EMI Passes Prototype, Fails Certification

A common real-world scenario:

· Prototype: 8 units

· EMI pre-scan: Pass

· Production: 3,000 units

· Certification: Fail at multiple frequencies

Root cause:

· Copper roughness variation

· Missing return path stitching

· PDN resonance shift

The design had no margin for variation.

Cost Impact of EMI Failures

EMI failures are expensive.

Typical costs include:

· Re-spins

· Shielding hardware

· Additional test cycles

· Delayed product launch

EMI fixes applied late cost 5–10× more than preventive design.

Procurement and Supply Chain Implications

Poor EMI design increases:

· Supplier dependence

· Material constraints

· Assembly sensitivity

Robust EMI design increases:

· Supplier flexibility

· Yield stability

· Long-term reliability

EMI is a supply-chain problem as much as a design problem.

Scaling EMI-Robust Designs from Prototype to Production

Prototypes hide EMI weaknesses.

To scale successfully:

· Validate EMI across multiple PCB lots

· Freeze stackup early

· Avoid last-minute layout changes

· Align design rules with fab capability

Scaling requires engineering discipline, not testing luck.

EMI / EMC Engineering Checklist

· Stackup optimized for low loop area

· Continuous return paths

· Controlled impedance with margin

· PDN resonance managed

· Via stitching applied correctly

· Assembly effects reviewed

This checklist prevents the majority of EMI failures.

How China 365PCB Supports EMI / EMC-Critical Projects

As an experienced OEM PCB manufacturer, 365PCB supports EMI-sensitive designs through:

· Stackup and return-path co-design

· Process-aware DFM reviews

· PDN and impedance validation

· Volume-aligned production control

Our goal is first-pass EMC success, not post-hoc fixes.

Final Thoughts: EMI Is a Design Discipline, Not a Test Result

Passing EMI testing is not about luck.

It is about controlling current paths, geometry, and variation from the first schematic onward.

Designs that succeed do so because EMI prevention was treated as a core engineering requirement—not an afterthought.

Engineering CTA (Low-Key, Professional)

If your product must pass EMI / EMC certification on the first attempt and scale reliably into volume production, early design review is essential.

Our engineering team can review stackups, routing strategies, and DFM risks before fabrication begins.

David Li

David Li is the Technical Communications Director at China 365PCB, with over 15 years of hands-on experience in the PCB and electronics manufacturing industry. Holding a Master’s degree in Electrical Engineering, he has worked extensively in both R&D and manufacturing roles at leading multinational electronics firms in Shenzhen before joining our team.

His expertise spans high-speed digital design, advanced packaging (HDI, Flex), and automotive-grade reliability standards. David is passionate about bridging the gap between design intent and production reality—a philosophy that aligns perfectly with 365PCB’s mission to deliver seamless, rapid, and fully-integrated manufacturing solutions.

Follow David’s insights on PCB technology trends and best practices here on the 365PCB Knowledge Hub.

English

English