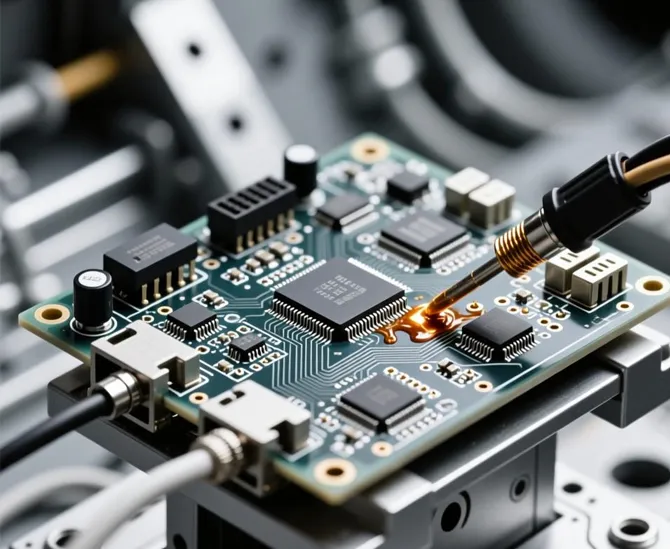

Why HDI PCBs Fail More Often Than Engineers Expect

HDI (High-Density Interconnect) PCB technology enables modern electronics to become smaller, faster, and more functional.

However, it also introduces some of the highest reliability and yield risks in PCB manufacturing.

Many HDI designs:

· Pass electrical simulation

· Pass early prototypes

· Fail unexpectedly during volume production or field operation

Common symptoms include:

· Intermittent opens after thermal cycling

· Via-in-pad reliability failures

· Yield collapse after scaling

· Cost escalation without performance gain

The reason is simple:

HDI PCBs amplify every weakness in design-for-manufacturing discipline.

What works marginally in conventional multilayer boards often fails catastrophically in HDI structures.

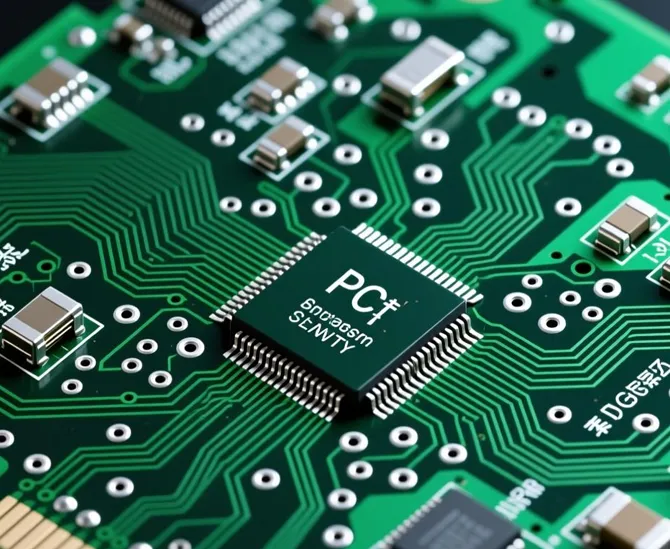

What Defines HDI PCB Technology

HDI PCBs are not defined by layer count alone.

They are defined by interconnect density and via architecture.

Key HDI features include:

· Microvias (typically ≤150 µm drill diameter)

· Blind and buried vias

· Via-in-pad structures

· Fine line and space routing

· Sequential lamination cycles

Each feature improves routing density—but also adds process complexity and yield risk.

Get to know more about HDI PCB technology: The Rise of HDI in Compact Electronics

Microvia Physics: Why Smaller Vias Are Harder to Build Reliably

Microvias appear electrically simple but are mechanically fragile.

3.1 Aspect Ratio Sensitivity

Unlike through-holes, microvias operate at extremely low aspect ratios.

Even small variations in laser drilling depth or dielectric thickness can cause:

· Incomplete via formation

· Poor copper coverage

· Early fatigue failure

3.2 Copper Plating Uniformity

Microvia reliability depends on uniform copper plating, especially at the via bottom.

Common failure mechanisms include:

· “Dog-bone” voids

· Thin copper at the via knee

· Stress concentration during thermal cycling

These defects often escape basic electrical testing.

Sequential Lamination: Where Yield Is Won or Lost

HDI PCBs almost always require multiple lamination cycles.

Each additional lamination step introduces:

· Registration risk

· Resin flow variability

· Accumulated internal stress

4.1 Registration Drift

As layer count increases, maintaining accurate layer-to-layer alignment becomes exponentially harder.

Misregistration causes:

· Partial via capture

· Reduced annular rings

· Increased open-circuit risk

4.2 Resin Flow and Void Formation

Inadequate resin flow during lamination can create:

· Resin starvation

· Microvoids around vias

· Delamination during reflow

These issues rarely appear in small prototype batches.

HDI Stackup Design: Electrical Goals vs Manufacturing Reality

HDI stackups must balance:

· Routing density

· Signal integrity

· Mechanical reliability

· Manufacturability

Common design mistakes:

· Excessive microvia stacking

· Overuse of via-in-pad without fill strategy

· Asymmetric stackups causing warpage

Stackup decisions directly determine yield stability.

Further reading: PCB Stackup Design The Structural Foundation of Signal Integrity, EMI Control, and Manufacturing Reliability

Via-in-Pad: Powerful but Dangerous

Via-in-pad is widely used in HDI designs to save space and improve routing.

However, it introduces significant DFA risk.

6.1 Fill and Cap Quality

Improper via fill causes:

· Solder wicking

· Void formation

· Pad collapse during reflow

6.2 Thermal Stress During Assembly

Via-in-pad structures experience high thermal gradients, increasing fatigue risk.

Designs that ignore assembly stress often fail after multiple reflow cycles.

DFM for HDI PCBs: Designing for Yield, Not Density

HDI DFM rules are fundamentally different from standard PCBs.

7.1 Practical DFM Guidelines

· Limit microvia stacking depth

· Avoid stacked vias unless absolutely required

· Use staggered vias when possible

· Define clear via fill and plating requirements

· Design with annular ring margin

Pushing density limits without DFM margin guarantees yield loss.

DFA: Assembly Challenges Unique to HDI Boards

HDI circuit boards are thinner, denser, and more sensitive to assembly variation.

8.1 Warpage and Coplanarity

Thin HDI boards are prone to:

· Warpage during reflow

· BGA coplanarity issues

· Head-in-pillow defects

8.2 Thermal Profile Sensitivity

Aggressive reflow profiles accelerate microvia fatigue.

Assembly must be tuned specifically for HDI structures.

Failure Case Study: HDI Design That Passed Prototype but Failed in Production

A real-world scenario:

· Prototype: 15 units, manual assembly

· Yield: 100%

· Production: 8,000 units

Failure observed:

· Intermittent opens after burn-in

· Failures increase with thermal cycling

Root cause:

· Stacked microvia fatigue

· Insufficient copper thickness at via knee

· No margin for lamination variation

The design was optimized for routing density—not reliability.

Cost Escalation Traps in HDI PCB Projects

HDI cost drivers are often underestimated.

Major contributors include:

· Additional lamination cycles

· Laser drilling time

· Via filling and planarization

· Increased scrap risk

Hidden cost risk:

A design that requires one extra lamination cycle can increase PCB cost by 30–50%.

Smart HDI design minimizes lamination steps.

Procurement and Supply Chain Impact

Not all PCB suppliers have true HDI capability.

Risks include:

· Limited laser drilling capacity

· Inconsistent plating quality

· Poor yield transparency

Single-source HDI designs increase long-term risk.

Early supplier qualification is critical.

Scaling HDI Designs from Prototype to Volume

HDI designs often fail during scaling due to:

· Process window narrowing

· Equipment differences

· Operator dependency

To scale successfully:

· Validate yield over multiple lots

· Lock critical parameters early

· Avoid last-minute density increases

Scaling is an engineering discipline—not a purchasing task.

Engineering Checklist for Reliable HDI PCBs

· Minimize stacked microvias

· Validate lamination cycles early

· Design with plating margin

· Define via fill requirements clearly

· Coordinate assembly profile with HDI structure

· Balance density with reliability

This checklist alone eliminates most HDI failures.

How China 365PCB Supports HDI PCB Projects

As a leading OEM PCB manufacturer, 365PCB supports HDI projects through:

· Stackup and via structure co-design

· Process-aware DFM reviews

· Controlled lamination and plating windows

· Assembly-aware reliability validation

Our focus is stable yield and long-term reliability, not just prototype success.

Final Thoughts: HDI Is a Reliability Problem First

HDI technology is not limited by design tools.

It is limited by process control, yield discipline, and reliability margin.

Designs that succeed do so because they respect manufacturing reality from day one.

Engineering CTA (Subtle, Professional)

If your HDI design must scale reliably from prototype to volume production, early DFM and DFA collaboration is essential.

Our engineering team is available to review via structures, stackups, and yield risks before fabrication begins.

David Li

David Li is the Technical Communications Director at China 365PCB, with over 15 years of hands-on experience in the PCB and electronics manufacturing industry. Holding a Master’s degree in Electrical Engineering, he has worked extensively in both R&D and manufacturing roles at leading multinational electronics firms in Shenzhen before joining our team.

His expertise spans high-speed digital design, advanced packaging (HDI, Flex), and automotive-grade reliability standards. David is passionate about bridging the gap between design intent and production reality—a philosophy that aligns perfectly with 365PCB’s mission to deliver seamless, rapid, and fully-integrated manufacturing solutions.

Follow David’s insights on PCB technology trends and best practices here on the 365PCB Knowledge Hub.

English

English