Why Signal Integrity Problems Rarely Appear as “Signal Integrity Problems”

Signal integrity (SI) failures almost never announce themselves clearly.

Instead of obvious errors, they appear as:

· Intermittent data corruption

· Reduced eye margin with no clear root cause

· Temperature-dependent failures

· EMI compliance issues

· Field failures that cannot be reproduced in the lab

Because these symptoms are indirect, signal integrity issues are often misdiagnosed as:

· Firmware bugs

· Component quality problems

· Power supply instability

· Assembly defects

In reality, signal integrity is the silent limiter of system reliability.

Most SI failures are not caused by a single mistake, but by multiple small discontinuities that accumulate across the signal path.

What Signal Integrity Really Means in Physical Hardware

At low speeds, signals behave like logic states.

At high speeds, they behave like electromagnetic waves.

Signal integrity describes how well a signal maintains its intended shape, timing, and amplitude from transmitter to receiver, despite:

· Impedance discontinuities

· Crosstalk

· Loss and dispersion

· Power/ground noise

· Manufacturing variation

Good signal integrity is not about perfection—it is about margin and robustness.

The Electrical Foundations of Signal Integrity

3.1 Transmission Line Behavior

When signal edge rates are fast relative to trace length, PCB traces must be treated as transmission lines.

This introduces:

· Reflections

· Standing waves

· Frequency-dependent loss

Ignoring transmission line effects is the root cause of many SI failures.

3.2 Return Path Continuity

Every signal has a return path.

If the return path is interrupted—by plane splits, vias, or layer transitions—the signal loop inductance increases, causing:

· Reflection

· Mode conversion

· EMI radiation

Return path discontinuity is one of the most common—and least understood—SI failure mechanisms.

Common Signal Integrity Design Mistakes

4.1 Treating SI as a Post-Layout Check

Many teams perform SI analysis only after routing is complete.

At that point, fixing SI problems often requires:

· Rerouting critical nets

· Changing stackup

· Adding costly workarounds

SI must guide layout—not validate it after the fact.

4.2 Over-Routing Differential Pairs

Differential signaling improves noise immunity, but it does not eliminate SI problems.

Poor differential routing introduces:

· Skew

· Asymmetry

· Common-mode noise

Differential pairs amplify manufacturing variation if not designed carefully.

4.3 Ignoring Power Integrity Interaction

Signal integrity and power integrity are inseparable.

A noisy power distribution network (PDN) introduces jitter and amplitude variation that appear as SI failures at the receiver.

Via Transitions: The Most Dangerous SI Discontinuity

Vias are unavoidable—but they are also one of the largest sources of SI degradation.

5.1 Stub Effects

Unused via stubs act as resonators, introducing:

· Reflections

· Frequency notches

· Eye closure

These effects worsen as data rates increase.

5.2 Reference Plane Changes

When a signal changes layers, the return path must follow.

If the reference plane changes without proper stitching vias, the signal experiences:

· Increased inductance

· Impedance discontinuity

· EMI radiation

Via transitions must be treated as three-dimensional structures, not simple connections.

Stackup Design and Its Impact on Signal Integrity

Stackup design — even in a simple 2 layer PCB stackup — determines:

· Impedance consistency

· Crosstalk behavior

· Return path quality

· EMI susceptibility

6.1 Poor Stackup = Permanent SI Limit

A poorly designed stackup cannot be fixed by routing skill alone.

Common stackup errors include:

· Too few reference planes

· Uneven plane pairing

· Long return path loops

Good SI starts with stackup—not routing.

Further reading: PCB Stackup Design The Structural Foundation of Signal Integrity, EMI Control, and Manufacturing Reliability

Manufacturing Variations That Affect Signal Integrity

Signal integrity simulations assume ideal geometry.

Manufacturing delivers statistical variation.

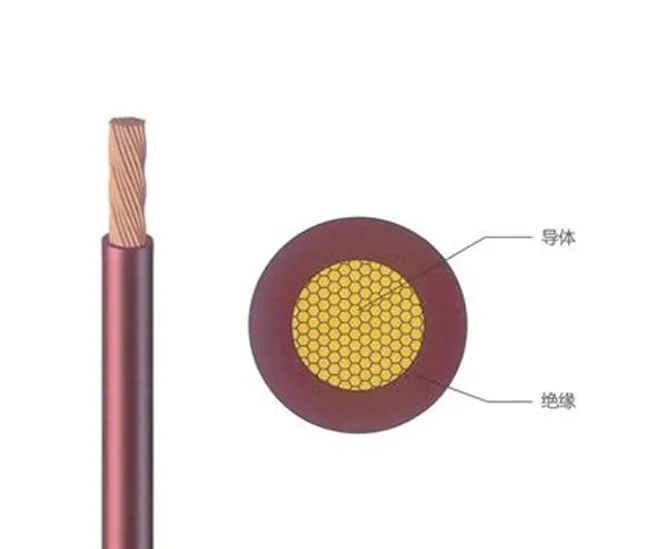

7.1 Copper Thickness and Roughness

Copper plating variation changes trace impedance and loss.

Surface roughness increases insertion loss and phase distortion at high frequencies.

7.2 Dielectric Thickness Variation

Prepreg thickness variation directly impacts impedance and timing.

Designs without margin experience unpredictable SI behavior across lots.

7.3 Etching Accuracy

As trace widths shrink, etching tolerance becomes a dominant SI factor.

Fine-line designs require conservative margins.

DFM: Designing for Signal Integrity Manufacturability

True SI robustness requires DFM discipline.

8.1 Practical DFM Rules for SI

· Finalize stackup before routing

· Use trace widths compatible with fab capability

· Minimize layer transitions

· Avoid unnecessary stubs

· Design with tolerance margin

Designs that push theoretical limits often fail in volume production.

DFA: Assembly Effects on Signal Integrity

PCB electronic assembly can significantly impact SI—especially at high data rates.

9.1 BGA and PDN Interaction

Solder voids and uneven copper distribution under BGAs disrupt reference planes, affecting return paths.

9.2 Reflow-Induced Material Stress

Thermal cycling alters dielectric properties and increases via fatigue risk, leading to long-term SI drift.

Ignoring DFA effects results in post-assembly performance degradation.

Failure Case Study: Signal Integrity Collapse After Scaling

A common real-world scenario:

· Prototype: 10 units, hand-assembled

· Performance: Clean eye diagrams

· Production: 5,000 units

Observed issues:

· Increased jitter

· Reduced eye height

· Random data errors

Root cause:

· Copper roughness variation

· Via stub resonance

· Assembly-induced plane discontinuity

The design had no margin for manufacturing reality.

Cost and Procurement Implications of Signal Integrity

Poor SI design increases cost through:

· PCB re-spins

· Over-spec materials

· Excessive layer count

· Debug and test time

Ironically, many SI failures cost far more to fix than to prevent.

Good SI design reduces:

· NRE

· Lead time

· Supplier dependence

Scaling Signal Integrity from Prototype to Mass Production

Prototypes hide SI weaknesses.

To scale successfully:

· Validate SI across multiple PCB lots

· Avoid single-source materials

· Freeze stackup early

· Align design rules with fab capability

Scaling is an engineering challenge—not a purchasing one.

Engineering Checklist for Robust Signal Integrity

· Stackup defined before layout

· Continuous return paths maintained

· Via transitions analyzed

· Power integrity considered

· DFM rules validated

· Assembly effects reviewed

This checklist eliminates the majority of SI-related failures.

How China 365PCB Supports Signal Integrity–Critical Designs

As an experienced OEM PCB manufacturer, 365PCB supports SI-critical projects through:

· Stackup and impedance co-design

· Process-aware SI simulation

· DFM/DFA reviews before fabrication

· Production-aligned validation strategies

Our focus is repeatable signal behavior, not lab-only success.

Final Thoughts: Signal Integrity Is About Margin, Not Perfection

Perfect waveforms exist only in simulation.

Real products succeed because they maintain adequate margin across variation, temperature, and scale.

Signal integrity is not a feature—it is a discipline.

Engineering CTA (Professional, Low-Key)

If your design operates at high data rates and must scale reliably from prototype to production, early signal integrity review confirms margin before fabrication begins.

Our engineering team is available to review stackups, routing strategies, and SI risks before release.

David Li

David Li is the Technical Communications Director at China 365PCB, with over 15 years of hands-on experience in the PCB and electronics manufacturing industry. Holding a Master’s degree in Electrical Engineering, he has worked extensively in both R&D and manufacturing roles at leading multinational electronics firms in Shenzhen before joining our team.

His expertise spans high-speed digital design, advanced packaging (HDI, Flex), and automotive-grade reliability standards. David is passionate about bridging the gap between design intent and production reality—a philosophy that aligns perfectly with 365PCB’s mission to deliver seamless, rapid, and fully-integrated manufacturing solutions.

Follow David’s insights on PCB technology trends and best practices here on the 365PCB Knowledge Hub.

English

English